Overview ..... 1 Simultaneous Sample and Hold ..... 2 Hardware Setup ..... 2 Card Connection ..... 2 Card Configuration ..... 2 CE Compliance ..... 3 DaqBook/100 Series & /200 Series and DaqBoard [ISA type] Configuration ..... 4 DaqBook/2000 Series and DaqBoard/2000 Series Configuration ..... 4 Software Setup ..... 4

DBK17 – Specifications ..... 5

#### **Reference Notes:**

- Refer to the *Power Requirements* section, in the *DBK Basics* document module, in regard to calculating system power requirements.

- Chapter 2, System Connections and Pinouts, includes pinouts for P1, P2, P3, and P4. Refer to the pinouts that are applicable to your system, as needed.

### **Overview**

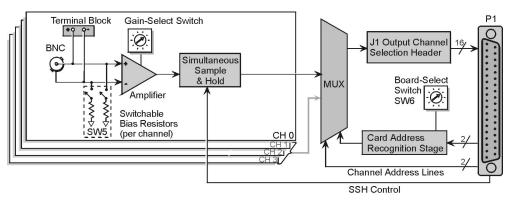

Each DBK17 simultaneous sample-and-hold (SSH) card provides 4 channels of voltage input to a LogBook or a Daq device system. Each of the 16 analog input channels can accept four DBK17 cards for a maximum of 256 analog input channels. The simultaneous sample-hold function is activated at the beginning of each channel scan and freezes all signals present on DBK17 inputs for the duration of the scan, allowing for non-skewed readings of all channels.

# A DBK17 channel should never be the first channel in a scan due to timing of the SSH line.

DBK17 features an instrumentation amplifier for each channel, with switch-selected gains of  $\times 1$ ,  $\times 10$ ,  $\times 200$  and  $\times 500$ . A socket is provided for a user-selected gain resistor for custom gain selection instead of the unity gain ( $\times 1$ ) setting.

Four separate sample-hold stages follow the 4 input stages. The outputs are connected to a 4-channel multiplexer stage. The enabled-output MUX allows up to 4 DBK17s to share a common analog input channel.

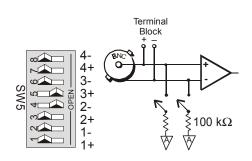

Input can be connected to a channel's BNC connector or terminal block. The differential inputs are provided with switchable100 K $\Omega$  bias resistors to analog common. User gain can be set to any value between unity and ×500 by installing a resistor in the user-location of each channel.

#### DBK17 Block Diagram

# Simultaneous Sample and Hold

Some applications require every channel in a scan group to be read *at the same instant*, as opposed to being read with a delay, e.g.,  $10 \ \mu$ s between channels. Simultaneous Sample and Hold (SSH) is a means of obtaining such instantaneous data on multiple channels while avoiding time-skew problems.

#### A sample case in which SSH is desirable:

A performance analysis of an engine is a classic example of a case in which SSH is desirable. In our engine analysis example data is gathered on the following parameters:

- cylinder pressure

- cylinder temperature

- piston strain

- piston stroke position

- valve position

- engine rpm

- vibration

For a more exact correlation of the data, it needs to be obtained at the same instant, without time-skew. By using SSH each input signal continuously passes through an instrumentation amplifier and into a sampleand-hold stage. When the sample enable line goes high, each channel's sample-and-hold stage will "freeze" the current analog value. The values for all channels are separately "latched" within 50 ns of each other. The signals are held [in a stable condition], while the multiplexer switches through all channels and sends the signals [one-by-one] to the acquisition device. At the device, the ADC digitizes each reading. The resulting data is a snapshot of conditions at a selected instant although the multiplexing and analog-todigital conversions are spread out over a longer interval. The simultaneous sample and hold circuit allows you to gather up to 256 simultaneous samples via sixty-four DBK17s.

# Hardware Setup

### **Card Connection**

The DBK17 is equipped with BNC connectors and terminal block connectors access to each of the four differential analog inputs. Note that the terminal block is a connection-option to the BNC connector.

### **Card Configuration**

#### **Factory Defaults**

- 100K bias resistors Enabled

- SSH Enabled. No disable option.

- Gain x1

#### Input Termination

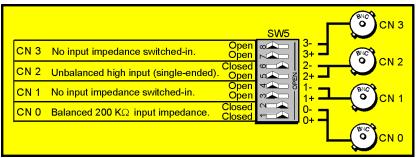

DBK17 provides two 100 K $\Omega$  bias resistors for each analog input. For balanced 200 K $\Omega$  input impedance, both resistors should be switched in. An 8-position DIP switch (SW5) can selectively engage the bias resistors. The input circuit and switch positions are shown in the figure. The switches must be in the closed position to engage the termination resistors. For unbalanced high input, only the (-) resistor should be used. If neither resistor is used, some external bias current path is required.

Input Impedance/Termination

**Examples of Bias Resistor Selection Options**

#### Gain Settings

On the card, each channel has a gain-set switch and holes for gain resistors labeled RG1 to RG4. The figure at the right shows gain values for switch settings 0 to 4, with 0 being equal to  $x_1$  and 4 being equal to  $x_500$ . If a custom gain is desired, the switch is set to position 0 and a gain resistor must be mounted and soldered onto the card. The value of the gain resistor is determined by the formula:

Gain Values Gain Switch 0 ×1 1 ×10 2 ×100 3 ×200 4 ×500 Setting Channel Gains

$R_{GAIN} = [40,000 / (Gain - 1)] - 50 \Omega$

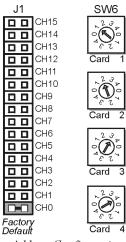

#### Address Configuration

As many as four DBK17s can be connected to each analog channel. With sixteen channels (and four inputs per DBK17) 256 inputs are possible. Since this is a daisy-chain interface, each card must have a unique address (channel and card number). Note that the default setting of SW6 is Card 1.

To configure the card, locate the  $16 \times 2$ -pin header (labeled J1) near the front of the board. The 16 jumper locations on this header are labeled CH0 through CH15. Place the jumper on the channel you wish to use. Only one jumper is used on a single card. Four cards in the daisy-chain can have the same channel number as long as their card number is unique.

Set switch SW6 for each of four DBK17s on a single channel. Verify that only one card in the system is set to a particular channel and card number.

Address Configuration

### **CE Compliance**

#### **Reference Notes:**

Should your data acquisition system need to comply with CE standards, refer to the CE Compliance section of chapter Signal Management.

# DaqBook/100 Series & /200 Series and DaqBoard [ISA type] Configuration

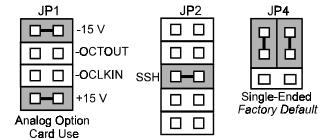

Use of the DBK17 requires setting jumpers in **DaqBook/100 Series & /200 Series devices** and **ISA-Type DaqBoards**.

1. If not using auxiliary power, ensure that the JP1 jumper is in the expanded analog mode (see figure).

Jumpers on DaqBook/100 Series, /200 Series, & ISA-Type DaqBoards

**Note**: The JP1 default position (above figure) is necessary to power the interface circuitry of the DBK17 via the internal +15 VDC power supply. See the following CAUTION regarding JP1.

**CAUTION** If using auxiliary power, for example a DBK32A or a DBK33, you must remove both JP1 jumpers. Refer to the section *Power Requirements* in the document module *DBK Basics* and the DBK32A and DBK33 modules as applicable.

2. Place the DaqBook/100 Series or DaqBook/200 Series device's JP2 jumper in the SSH position.

**CAUTION** Do not use an external voltage reference for DAC1. Applying an external voltage reference for DAC1 when using SSH output will result in equipment damage due to a conflict on P1, pin #26.

3. For DaqBook/100, /112 and /120 only, ensure that the JP4 jumper is in single-ended mode.

### DaqBook/2000 Series and DaqBoard/2000 Series Configuration

No hardware configurations are required for the DaqBook/2000 Series or DaqBoard/2000 Series devices.

# **Software Setup**

Reference Notes:

> DaqView users - Refer to the chapter *DBK Setup in DaqView*.

➤ LogView users - Refer to the chapter *DBK Setup in LogView*.

# DBK17 – Specifications

| Name/Function: Simultaneous Sample-Hold Card<br>Number of Channels: 4<br>Input Connections: 4 BNC connectors, 4 screw-terminal sets<br>Output Connector: DB37 male, which mates with P1 using CA-37-x<br>cable<br>Number of Cards Addressable: 64<br>Input Type: Differential<br>Voltage Input Ranges:<br>0 to $\pm 5000 \text{ mVDC}$<br>0 to $\pm 5000 \text{ mVDC}$<br>0 to $\pm 500 \text{ mVDC}$<br>0 to $\pm 500 \text{ mVDC}$<br>0 to $\pm 500 \text{ mVDC}$<br>0 to $\pm 25 \text{ mVDC}$<br>0 to $\pm 10 \text{ mVDC}$<br>Input Amplifier Slew Rate: 12 V/µs minimum<br>Acquisition Time:<br>0.6 µs (10 V excursion to 0.1%)<br>0.7 µs (10 V excursion to 0.1%)<br>0.7 µs (10 V excursion to 0.01%)<br>Channel-to-Channel Aperture Uncertainty: 50 ns<br>Output Droop Rate: 0.1 µV/µs<br>Input Gains: $\times 1$ , $\times 10$ , $\times 100$ , $\times 200$ , $\times 500$ & User-Set<br>Input Offset Voltage: 500 µV + 5000/G maximum (nullable)<br>Input Offset Drift: $\pm 5 + 100/G$ µV/°C maximum<br>Input Bias Current: 100 pA maximum | Gain Errors: $0.04\%$ @ ×1 $0.1\%$ @ ×10 $0.2\%$ @ ×100 $0.2\%$ @ ×100 $0.4\%$ @ ×200 $1.0\%$ @ ×500   Gain vs Temperature:   ×1 @ ±20 ppm/°C   ×10 @ ±20 ppm/°C   ×10 @ ±20 ppm/°C   ×200 @ ±60 ppm/°C   ×200 @ ±60 ppm/°C   ×500 @ ±100 ppm/°C   ×00 to ±0.015% full-scale   ×100 to ±0.025% full-scale   ×200 to ±0.025% full-scale   ×500 to ±0.045% full-scale   ×500 to ±0.045% full-scale   ×500 to ±0.045% full-scale   Common-Mode Rejection Ratio   (CMRR):   70 dB minimum @ ×1   87 dB minimum @ ×10   100 dB minimum @ ×100   100 dB minimum @ ×200 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input Offset Drift: ±5 + 100/G µV/°C maximum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |